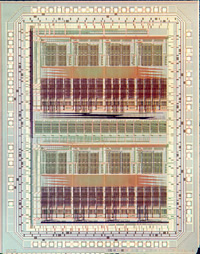

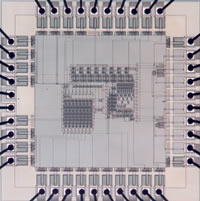

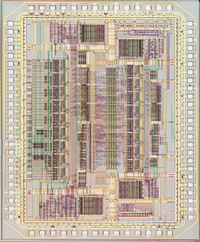

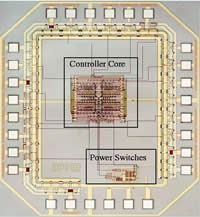

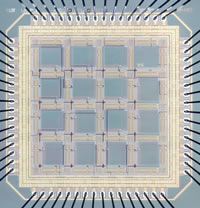

16 Oscillators and 24 phase detectors form a distributed, symmetric phase-locked loop that is guaranteed to lock with the phases aligned, and generate a 1.3 GHz clock over the entire 3mm x 3 mm chip. Fabricated in a 0.35 micron TSMC process, the chip consumed 130 mA and 3V.