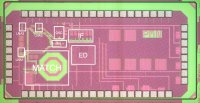

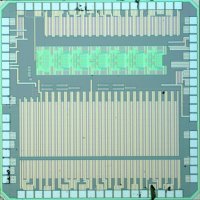

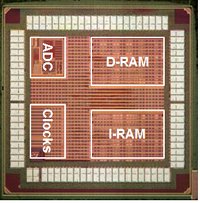

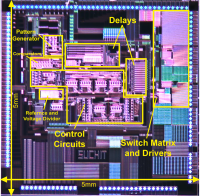

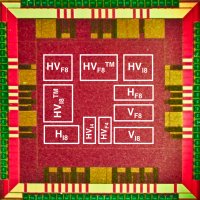

Transform engine is a critical part of the video codec and increased coding efficiency often comes at the cost of increased complexity in the transform module. In this work we propose a shared-reconfigurable transform engine for H.264/AVC and VC-1 video coding standards, using the structural similarity and symmetry of the transforms for H.264/AVC and VC-1. An approach to eliminate the need for an explicit transpose memory in 2D transforms is proposed. Data dependency is exploited to reduce power consumption. Ten different versions of the transform engine, such as with and without hardware sharing, with and without transpose memory, are implemented in the design. The design is fabricated using commercial 45nm CMOS technology and all implemented versions are verified. The shared-reconfigurable transform engine without transpose memory supports Quad Full-HD (3840x2160) video encoding at 30fps, while operating at 0.52V, with measured power of 214 µW.