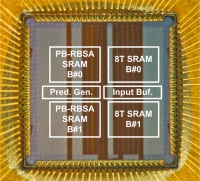

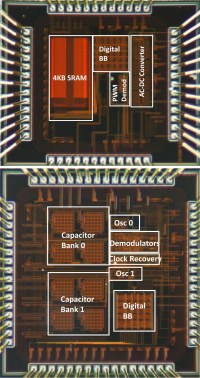

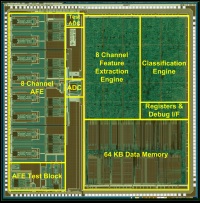

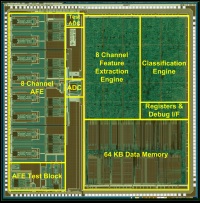

An 8-channel scalable EEG acquisition SoC is presented to continuously detect and record patient-specific seizure onset activities from scalp EEG. The SoC integrates 8 high-dynamic range Analog Front-End (AFE) channels, a machine-learning seizure classification processor and a 64KB SRAM. The classification processor exploits the Distributed Quad-LUT filter architecture to minimize the area while also minimizing the overhead in power×delay. The AFE employs a Chopper-Stabilized Capacitive Coupled Instrumentation Amplifier to show NEF of 5.1 and noise RTI of 0.91µVrms for 0.5-100Hz bandwidth. The classification processor adopts a support-vector machine as a classifier, with a GBW controller that gives real-time gain and bandwidth feedback to AFE to maintain accuracy. The SoC is verified with the Children's Hospital Boston-MIT EEG database as well as with rapid eye blink pattern detection test. The SoC is implemented in 0.18µm 1P6M CMOS process occupying 25 sq.mm, and it shows an accuracy of 84.4% in eye blink classification test, at 2.03µJ/classification energy efficiency. The 64 KB on chip memory can store up to 120 seconds of raw EEG data.