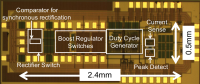

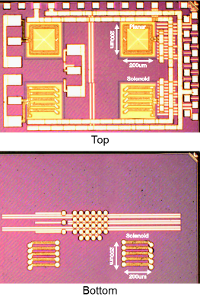

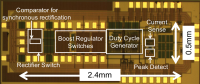

The growing number of IoT devices calls for new solutions for efficient power delivery that are also more scalable than wired systems. Energy harvesting in an indoor environment is usually limited in output power, while wireless charging using near-field magnetic coupling requires close proximity between the Tx and Rx. In order to recharge these devices without affecting their operation, this work proposes using portable transmitters by adding wireless charging capability to smartphones, for example. In such a system, maximizing system efficiency throughout the entire charging cycle instead of output power becomes the primary concern. The receiver IC consists of a resonant rectifier implemented using synchronously driven, on-chip switches and off-chip passives that reduces switching losses and lowers switch voltage stress. The system also implements a maximum system efficiency-tracking loop that requires no explicit communication with the Tx. The receiver IC includes analog sense circuitry for the tracking loop and a boost regulator at the output of the rectifier. The analog measurements are digitized by an off-chip microcontroller, which calculates the efficiency and moves the operating point of the system towards the maximum efficiency-point by changing the duty cycle input of the boost regulator.