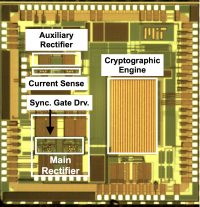

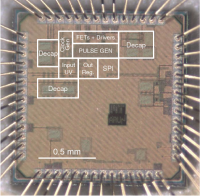

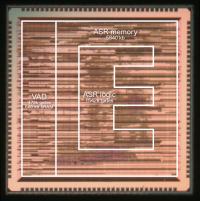

In ultrasound imaging systems, a large number of waveforms are acquired in parallel from a transducer array. To facilitate the move to portable ultrasound systems with real-time displays, we implemented a low-power digital beamformer ASIC in 65 nm bulk CMOS technology. We describe three operating modes that provide a run-time tradeoff between image quality and system power consumption. A sliding window approach eliminates the need for an on-chip SRAM, which reduces area and power. The chip generates four output pixels per clock cycle from eight channel of input data, allowing 30 frames per second at 1.92 MHz. The prototype test chip is operational down to a core supply voltage of 0.49 V, with a measured power of 185 uW in real-time operation at 0.52 V.