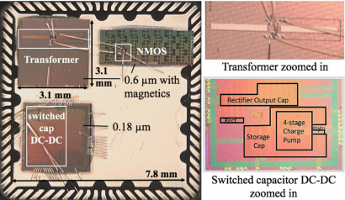

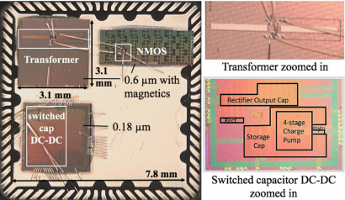

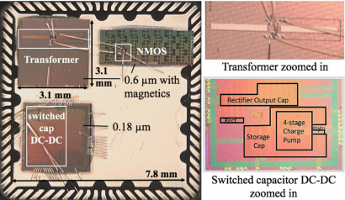

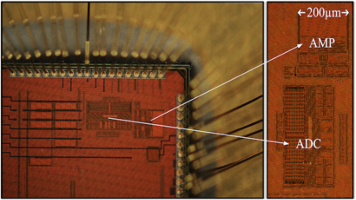

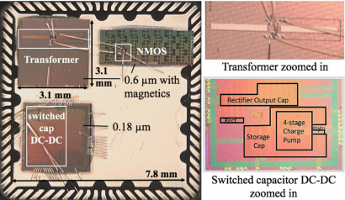

Thermal energy harvesting systems use boost converters for high-efficiency low voltage operation, but lack the ability for low voltage startup without off-chip transformers. We present a cold start system that uses integrated magnetics instead of external transformers in a Meissner Oscillator to start up from ultra low voltages, with a switched capacitor DC-DC circuit for additional voltage gain. The oscillator analysis with on-chip magnetics allows device co-optimization for low voltage operation, despite 1000x lower inductance values than off-chip transformers. Co-optimized on-chip transformer and depletion-mode NMOS start up from 25 mV driven directly by a sourcemeter, or 50 mV with a 4.7 Ω series resistance, for the lowest integrated electrical startup. The co-packaged system provides proof of concept for integration with boost converter circuits on a single die to have a fully-integrated low voltage startup solution for thermal energy harvesting applications, without using off-chip transformers.