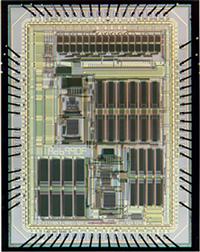

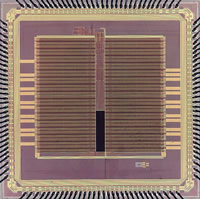

The DSRCP utilizes a dynamically-reconfigurable datapath to implement a variety of public key cryptographic primitives and algorithms including large integer arithmetic (8 - 1024), both prime and binary Galois Field arithmetic (GF(2^8) - GF(2^1024), and GF(p) for 2^8 < p < 2^1024), and Elliptic Curve arithmetic over both integer and binary Galois fields.