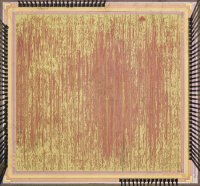

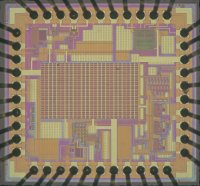

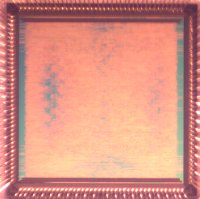

A 1 Mbps 916.5 MHz OOK transceiver for wireless sensor networks has been designed in a 0.18-µm CMOS process. The RX has an envelope detection based architecture with a highly scalable RF front end. The RX power consumption scales from 0.5 mW to 2.6 mW, with an associated sensitivity of -37 dBm to -65 dBm at a BER of 10

-3. The TX consumes 3.8 mW to 9.1 mW with output power from -11.4 dBm to -2.2 dBm. The RX achieves a startup time of 2.5 µs, allowing for efficient duty cycling.