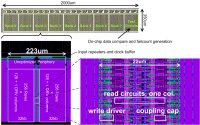

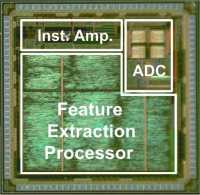

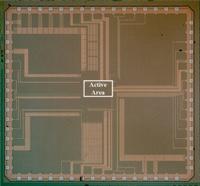

The IC is fabricated in 180nm 5M2P CMOS and operates at 1V. It includes a low-noise instrumentation amplifier for electroencephalograph (EEG) acquisition, an ADC, and a custom digital processor. The instrumentation amplifier uses a chopper-stabilized first stage with a power consumption of 3.5µW and a noise PSD of 130nV/sqrt(Hz). Its input impedance is >700MOhm making it suitable for surface EEG acquisition using Ag/AgCl electrodes. The ADC consumes 250nJ for each 12-bit conversion (10.6 ENOB). The processor includes a decimation filter and a spectral-analysis FIR filter bank to extract spectra-energy features for continuous seizure detection.