A 100µW 10Mb/s eTextiles Transceiver for Body Area Networks with remote Battery Power

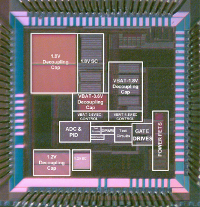

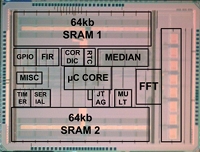

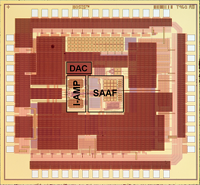

A transceiver for communicating over an electronic textiles medium is implemented for body area networks. A supply-rail-coupled differential signaling scheme permits time-sharing of the eTextiles medium between communication and remote powering circuits. Fabricated in 0.18µm CMOS and operating at 0.9V, the chip consumes 110µW at a data rate of 10Mb/s over a 1m fabric link. This results in 20-100× higher energy efficiency than state-of-the-art wireless and body-coupled communication systems.