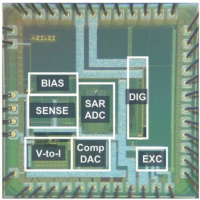

This paper reports the first chip-based demonstration (at any frequency) of a CMOS front-end that generates and receives electromagnetic waves with rotating wave phase front (namely orbital angular momentum or OAM). The chip, based on a uniform circularly placed patch antenna array at 0.31THz, transmits reconfigurable OAM modes, which are digitally switched among the m=0 (plane wave), +1 (left-handed), -1 (right-handed) and superposition (+1)+(-1) states. The chip is also reconfigurable into a receiver mode that identifies different OAM modes with >10dB rejection of unintended modes. The array, driven by only one active path, has a measured EIRP of -4.8dBm and consumes 154mW of DC power in the OAM source mode. In the receiver mode, it has a measured conversion loss of 30dB and consumes 166mW of DC power. The output OAM beam profiles and mode orthogonality are experimentally verified and a full silicon OAM link is demonstrated.